# HT45B0F SPI-to-UART Bridge

### Features

- Operating Voltage

- f<sub>CLKI</sub>= 12MHz: 2.0V~5.5V

- f<sub>CLKI</sub>= 16MHz: 2.7V~5.5V

- f<sub>CLKI</sub>= 20MHz: 4.5V~5.5V

- Glueless slave SPI interface to Holtek's MCU

- Full-duplex, Universal Asynchronous Receiver and Transmitter (UART) communication

- 8 or 9 bit character length

- Even, odd or no parity options

- One or two stop bits

- Baud rate generator with 8-bit prescaler

- Parity, framing, noise and overrun error detection

- Support for interrupt on address detect

- Address Detect Interrupt last character bit=1

- Transmitter and receiver enabled independently

- 4-byte deep FIFO receiver data buffer

# **General Description**

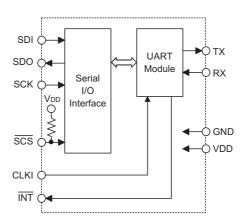

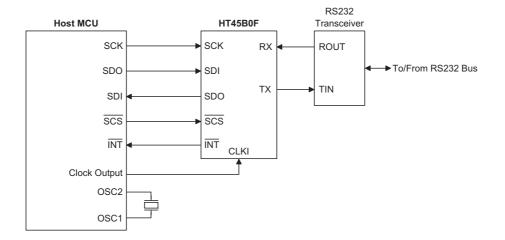

The HT45B0F is microcontroller peripheral device to implement SPI-to-UART data conversions. The UART module can operate in full-duplex mode with an interrupt output capability to the host microcontroller.

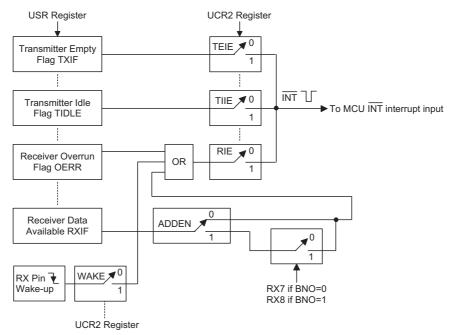

- Transmit and Receive Multiple Interrupt Generation Sources:

- Transmitter Empty

- Transmitter Idle

- Receiver Full

- Receiver Overrun

- Address Mode Detect

- TX pin is high impedance when the UART transmit module is disabled

- RX pin is high impedance when the UART receive module is disabled

- CMOS clock input, CLKI, up to 20MHz at 5V operating voltage

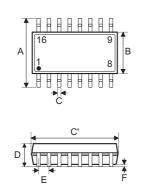

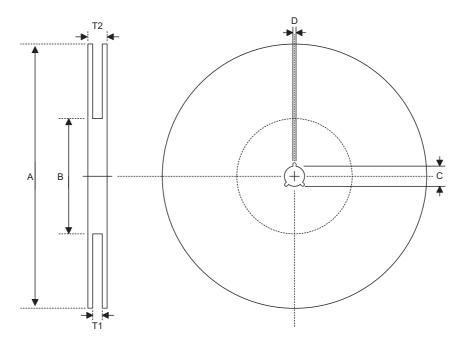

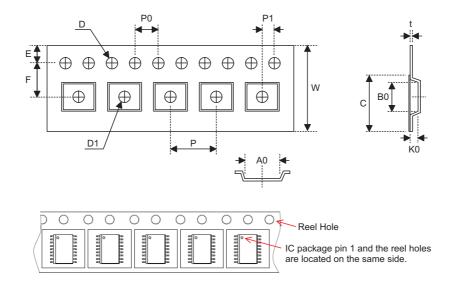

- 16-pin NSOP package

Possible application could include data communication networks between microcontrollers, low-cost data links between PCs and peripheral devices, portable and battery operated devices, factory automation and process control to name but a few.

### **Block Diagram**

# **Pin Assignment**

|           |   | <u> </u> |    | 1     |  |  |  |  |

|-----------|---|----------|----|-------|--|--|--|--|

| SDI 🗆     | 1 | $\cup$   | 16 | рис   |  |  |  |  |

| SDO 🗆     | 2 |          | 15 | □ мс  |  |  |  |  |

| SCK 🗆     | 3 |          | 14 | □ мс  |  |  |  |  |

| SCS 🗆     | 4 |          | 13 | □ мс  |  |  |  |  |

| CLKI 🗆    | 5 |          | 12 | ¦⊐ тх |  |  |  |  |

|           | 6 |          | 11 |       |  |  |  |  |

| NC 🗆      | 7 |          | 10 |       |  |  |  |  |

| NC 🗆      | 8 |          | 9  | □ vss |  |  |  |  |

|           |   |          |    |       |  |  |  |  |

| HT45B0F   |   |          |    |       |  |  |  |  |

| 16 NSOP-A |   |          |    |       |  |  |  |  |

# **Pin Description**

| Pin Name | I/O | Description                                                                                                                               |

|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------|

| SDI      | I   | Serial I/O data input<br>SDI is high impedance when SCS = HIGH                                                                            |

| SDO      | 0   | Serial I/O data output.<br>SDO is high impedance when $\overline{SCS}$ = HIGH                                                             |

| SCK      | I   | Serial I/O clock input<br>SCK is high impedance when $\overline{SCS}$ = HIGH                                                              |

| SCS      | I   | Serial I/O Chip select input, active low<br>SCS has an internal pull-high resistor.                                                       |

| CLKI     | I   | External clock input                                                                                                                      |

| INT      | 0   | Interrupt output (CMOS output structure).<br>Connected to the MCU's external interrupt input                                              |

| RX       | I   | UART RX Pin<br>If UARTEN = 1 and RXEN = 1, then RX is the UART serial data input<br>If UARTEN = 0 or RXEN = 0, then RX is high impedance  |

| тх       | 0   | UART TX Pin<br>If UARTEN = 1 and TXEN = 1, then TX is the UART serial data output<br>If UARTEN = 0 or TXEN = 0, then TX is high impedance |

| VDD      | _   | Positive power supply                                                                                                                     |

| VSS      |     | Negative power supply, ground                                                                                                             |

| NC       |     | No connection                                                                                                                             |

# Absolute Maximum Ratings

| Supply VoltageV_SS=0.3V to V_SS+6.0V    | Storage Temperature50°C to +150°C  |

|-----------------------------------------|------------------------------------|

| Input VoltageV_{SS}=0.3V to V_{DD}+0.3V | Operating Temperature40°C to +85°C |

| I <sub>OL</sub> Total35mA               | I <sub>OH</sub> Total35mA          |

| Total Power Dissipation135mW            |                                    |

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

# D.C. Characteristics

| Sym-             | Dura                             |                 | Test Conditions                                                                                                                                                                                      |                    | _    |                    |      |

|------------------|----------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|--------------------|------|

| bol              | Parameter                        | V <sub>DD</sub> | Conditions                                                                                                                                                                                           | Min.               | Тур. | Max.               | Unit |

|                  |                                  |                 | f <sub>CLKI</sub> = 12MHz                                                                                                                                                                            | 2.0                |      | 5.5                | V    |

| V <sub>DD</sub>  | Operating Voltage                | _               | f <sub>CLKI</sub> = 16MHz                                                                                                                                                                            | 2.7                |      | 5.5                | V    |

|                  |                                  |                 | f <sub>CLKI</sub> = 20MHz                                                                                                                                                                            | 4.5                |      | 5.5                | V    |

|                  |                                  | 2.0V            | f <sub>CLKI</sub> =12MHz, SCK=f <sub>CLKI</sub> /4,<br>Output no load                                                                                                                                | _                  |      | 0.8                | mA   |

| I <sub>DD1</sub> | Operating Current                | 2.7V            |                                                                                                                                                                                                      | _                  |      | 1.0                | mA   |

| 001              | (SPI Enabled, UART disabled)     | 3.3V            | f <sub>CLKI</sub> =16MHz, SCK=f <sub>CLKI</sub> /4,<br>Output no load                                                                                                                                | _                  |      | 1.5                | mA   |

|                  |                                  | 5.0V            |                                                                                                                                                                                                      | _                  |      | 2.0                | mA   |

|                  |                                  | 2.0V            | f <sub>CLKI</sub> =6MHz, SCK=f <sub>CLKI</sub> /4,                                                                                                                                                   | _                  |      | 4.0                | mA   |

| :                | Operating Current                | 2.7V            | Output no load                                                                                                                                                                                       | _                  |      | 4.5                | mA   |

| I <sub>DD2</sub> | (SPI enabled, UART enabled)      | 3.3V            | f <sub>CLKI</sub> =12MHz, SCK=f <sub>CLKI</sub> /4,                                                                                                                                                  | _                  |      | 5.0                | mA   |

|                  |                                  | 5.0V            | Output no load                                                                                                                                                                                       | _                  |      | 6.0                | mA   |

| _                | Standby Current                  | 2.0V            | $\label{eq:scalar} \begin{array}{l} f_{CLKI} = 12MHz, \ SCK = f_{CLKI}/4, \\ \overline{SCS} = V_{DD}, \ UARTEN = 0, \\ TXEN = 1, \ RXEN = 1, \ SDI = H, \\ RX = H, \ Output \ no \ load \end{array}$ |                    | _    | 0.6                | μΑ   |

|                  | (SPI disabled, UART disabled)    | 2.7V            | f <sub>CLKI</sub> =16MHz, SCK=f <sub>CLKI</sub> /4,                                                                                                                                                  | _                  |      | 0.6                | μA   |

|                  |                                  | 3.3V            | SCS=V <sub>DD</sub> , UARTEN=0,<br>TXEN=1, RXEN=1, SDI=H,                                                                                                                                            | _                  |      | 0.6                | μA   |

|                  |                                  | 5.0V            | RX=H, Output no load                                                                                                                                                                                 | _                  |      | 0.6                | μA   |

| V <sub>IL1</sub> | Input Low Voltage for I/O Ports  | _               | _                                                                                                                                                                                                    | 0                  |      | 0.3V <sub>DD</sub> | V    |

| V <sub>IH1</sub> | Input High Voltage for I/O Ports | _               | _                                                                                                                                                                                                    | 0.7V <sub>DD</sub> |      | V <sub>DD</sub>    | V    |

| V <sub>IL2</sub> | Input Low Voltage for CLKI       | _               | _                                                                                                                                                                                                    | 0                  |      | 0.3V <sub>DD</sub> | V    |

| V <sub>IH2</sub> | Input High Voltage for CLKI      | _               | _                                                                                                                                                                                                    | $0.7V_{DD}$        | _    | V <sub>DD</sub>    | V    |

|                  |                                  | 2.0V            |                                                                                                                                                                                                      | 0.5                | 1.0  | _                  | mA   |

| 1                | 1/0 Dart Sink Current            | 2.7V            | V <sub>O</sub> =0.1V <sub>DD</sub>                                                                                                                                                                   | 1.0                | 2.0  | _                  | mA   |

| I <sub>OL</sub>  | I/O Port Sink Current            | 3.3V            |                                                                                                                                                                                                      | 4.0                | 10.0 | _                  | mA   |

|                  |                                  | 5.0V            |                                                                                                                                                                                                      | 10.0               | 25.0 | _                  | mA   |

|                  |                                  | 2.0V            |                                                                                                                                                                                                      | -0.4               | -0.8 | _                  | mA   |

| 1                | 1/O Dart Source Current          | 2.7V            |                                                                                                                                                                                                      | -1.0               | -2.0 | _                  | mA   |

| I <sub>OH</sub>  | I/O Port Source Current          | 3.3V            | V <sub>O</sub> =0.9V <sub>DD</sub>                                                                                                                                                                   | -4.0               | -5.0 | _                  | mA   |

|                  |                                  |                 |                                                                                                                                                                                                      | -5.0               | -8.0 | _                  | mA   |

|                  |                                  | 2.0V            |                                                                                                                                                                                                      | 30                 | 90   | 150                | kΩ   |

| P                | Pull-high Resistance for         | 2.7V            | ]                                                                                                                                                                                                    | 20                 | 60   | 100                | kΩ   |

| R <sub>PH</sub>  | SCS only                         | 3.3V            |                                                                                                                                                                                                      | 15                 | 45   | 75                 | kΩ   |

|                  |                                  | 5.0V            |                                                                                                                                                                                                      | 10                 | 30   | 50                 | kΩ   |

Ta=25°C

# A.C. Characteristics

| 0                 | Description                                     | Т               | est Conditions |        | Тур. | Max.  | Unit |

|-------------------|-------------------------------------------------|-----------------|----------------|--------|------|-------|------|

| Symbol            | Parameter                                       | V <sub>DD</sub> | Conditions     | Min.   |      |       |      |

|                   | V <sub>DD</sub> Slew Rate for POR               | _               |                | 0.0034 | _    | _     | V/ms |

|                   |                                                 | 2.0V            | _              | 400    |      | 12000 | kHz  |

| f <sub>CLKI</sub> | System Clock<br>(External Clock Input)          | 2.7V            |                | 400    | _    | 16000 | kHz  |

|                   |                                                 | 5.0V            |                | 400    |      | 20000 | kHz  |

|                   |                                                 | 2.0V            |                | 83.3   |      |       | ns   |

| 1                 | SCK Deried (to be to )                          | 2.7V            |                | 62.5   | _    |       | ns   |

| t <sub>CP</sub>   | SCK Period (t <sub>CH</sub> + t <sub>CL</sub> ) | 3.0V            |                | 62.5   |      | _     | ns   |

|                   |                                                 | 5.0V            |                | 50.0   |      |       | ns   |

|                   |                                                 | 2.0V            |                | 37     |      |       | ns   |

| 1                 |                                                 | 2.7V            |                | 28     |      |       | ns   |

| t <sub>CH</sub>   | SCK High Time                                   | 3.0V            | _              | 28     | _    |       | ns   |

|                   |                                                 | 5.0V            |                | 22     |      | _     | ns   |

| t <sub>CL</sub>   | SCK Low Time                                    | 2.0V            |                | 37     |      |       | ns   |

|                   |                                                 | 2.7V            |                | 28     |      |       | ns   |

|                   |                                                 | 3.0V            |                | 28     |      |       | ns   |

|                   |                                                 | 5.0V            |                | 22     |      |       | ns   |

|                   |                                                 | 2.0V            |                | 667    | _    |       | ns   |

|                   |                                                 | 2.7V            |                | 500    |      |       | ns   |

| t <sub>CSW</sub>  | SCS High Pulse Width                            | 3.0V            | —              | 500    | _    |       | ns   |

|                   |                                                 | 5.0V            |                | 400    |      |       | ns   |

| t <sub>CSS</sub>  | SCS to SCK Setup Time                           | _               |                | 100    |      |       | ns   |

| t <sub>CSH</sub>  | SCS to SCK Hold Time                            | _               | _              | 0      | _    |       | ns   |

| t <sub>SDS</sub>  | SDI to SCK Setup Time                           | _               |                | 100    | _    | _     | ns   |

| t <sub>SDH</sub>  | SDI to SCK Hold Time                            | _               |                | 0      | _    |       | ns   |

| t <sub>R</sub>    | SPI Output Rise Time                            | _               |                |        | 10   | _     | ns   |

| t <sub>F</sub>    | SPI Output Fall Time                            | _               | _              | _      | 10   |       | ns   |

| t <sub>W</sub>    | SPI Data Output Delay Time                      | _               |                | 0      | _    |       | ns   |

### **Functional Description**

The HT45B0F is full-duplex asynchronous serial communications UART interface that enables communication with external devices that contain a serial interface. The UART function has many features and can transmit and receive data serially by transferring a frame of data with eight or nine data bits per transmission as well as being able to detect errors when the data is overwritten or incorrectly framed. All data transmissions and receptions between MCU and HT45B0F including UART commands are conducted along this interconnected SPI interface. The UART function control is executed by the MCU using its SPI Master serial interface. The device contains its own independent interrupt which can be used to indicate when a data reception occurs or when a data transmission has terminated.

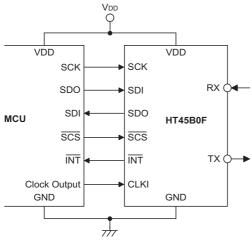

For Example Connection

#### **SPI Interface**

The MCU communicates with the device via an internal SPI interface. The SPI interface on this device is comprised of four signals:  $\overline{SCS}$  (SPI Chip Select), SCK (SPI Clock), SDI (Serial Data Input) and SDO (Serial Data Output). The SPI master, which is the MCU, asserts  $\overline{SCS}$  by pulling it low to start the data transaction cycle. When the first 8 bits of data are transmitted,  $\overline{SCS}$  should not return to a high level. Instead,  $\overline{SCS}$  must remain at a low level until the whole 16-bit data transaction is com-

pleted. If  $\overline{SCS}$  is de-asserted, that is returned to a high level before the 16-bit data transaction is completed, all data bits will be discarded by the device SPI slave.

#### **SPI** Timing

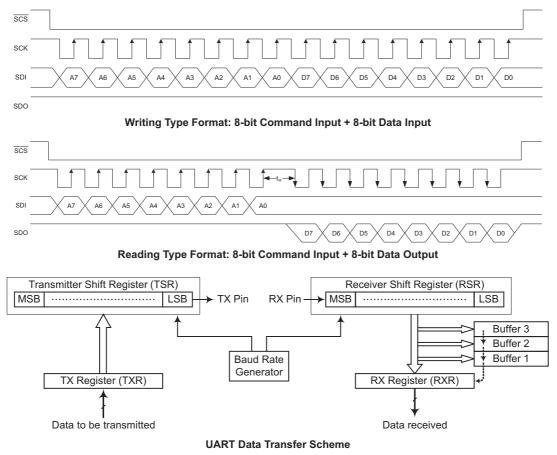

Both read and write operations are conducted along the SPI common interface with the following format:

- Write Type Format: 8-bit command input + 8-bit data input

- Read Type Format: 8-bit command input + 8-bit data

output

To initiate a data transaction, the MCU master SPI needs to pull  $\overline{SCS}$  to a low level first and then also pull SCK low. The input data bit on SDI should be stable before the next SCK rising edge, as the device will latch the SDI status on the next SCK rising edge. Regarding the SDO line, the output data bit will be updated on the SCK falling edge. The master needs to obtain the line status before the next SCK falling edge.

There are 16 bits of data transmitted and/or received by the SPI interface for each transaction. Each transaction consists of a command phase and a data phase. When  $\overline{\text{SCS}}$  is high, the SPI interface is disabled and SDO will be set to a high impedance state.

After a complete transaction has been implemented, which requires 16 SCK clock cycles, the master needs to set  $\overline{\text{SCS}}$  to a high level in preparation for the next data transaction.

For write operations, the device will begin to execute the command only after it receives a 16-bit serial data sequence and when the  $\overline{\text{SCS}}$  has been set high again by the master.

For read operations, the device will begin to execute the command only after it receives an 8-bit read command after which it will be ready to output data. If necessary, the master can de-assert the  $\overline{\text{SCS}}$  pin to abort the transaction at any time which will cause any data transactions to be abandoned.

#### **Pin Interfacing**

The UART has two pins known as TX and RX. The TX pin is the UART transmitter serial data output pin if the corresponding control bits named UARTEN in UCR1 register and TXEN in UCR2 register are set to 1. If the control bit UARTEN or TXEN is equal to zero, the TX pin is in the state of high impedance. Similarly, the RX pin is the UART receiver serial data input pin if the corresponding control bits named UARTEN and RXEN in UCR1 and UCR2 registers are set to 1. If the control bit UARTEN or RXEN is equal to zero, the RX pin is in the state of high impedance.

#### **UART Data Transfer Scheme**

The following block diagram shows the overall data transfer structure arrangement for the UART. The actual data to be transmitted from the MCU is first transferred to the TXR register by the application program. The data will then be transferred to the Transmitter Shift Register named TSR from where it will be shifted out, LSB first, onto the TX pin at a rate controlled by the Baud Rate Generator. Only the TXR register is accessible to the application program, the Transmitter Shift Register is not mapped into the Data Memory area and is inaccessible to the application program.

Data to be received by the UART is accepted on the RX pin, from where it is shifted in, LSB first, to the Receiver Shift Register named RSR at a rate controlled by the Baud Rate Generator. When the shift register is full, the data will then be transferred from the shift register to the internal RXR register, where it is buffered and can be manipulated by the application program. Only the RXR register is accessible to the application program, the Receiver Shift Register is not mapped into the Data Memory area and is inaccessible to the application program. It should be noted that the actual register for data transmission and reception, although referred to in the text, and in application programs, as separate TXR and RXR registers, only exists as a single shared register physically. This shared register known as the TXR/RXR register is used for both data transmission and data reception.

#### **UART Commands**

There are both read and write commands. For reading and writing to registers both command and address information is contained within a single byte. The format for reading and writing is shown in the following table.

| Command Type   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Read FIFO      | 0     | 0     | 0     | 0     | 0     | Х     | Х     | Х     |

| Read Register  | 0     | 0     | 0     | 1     | 0     | A2    | A1    | A0    |

| Write FIFO     | 0     | 0     | 0     | 0     | 1     | Х     | Х     | х     |

| Write Register | 0     | 0     | 0     | 1     | 1     | A2    | A1    | A0    |

Note: "X" here stands for "don't care"

#### **UART Status and Control Registers**

There are six registers associated with the UART function. The USR, UCR1, UCR2 and UCR3 registers control the overall function, while the BRG register controls the Baud rate. The actual data to be transmitted and received on the serial interface is managed through the TXR/RXR data register.

| A[2:0]      | Name   | Reset     | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|--------|-----------|--------|-------|-------|-------|-------|-------|-------|-------|

| 00H         | USR    | 0000 1011 | PERR   | NF    | FERR  | OERR  | RIDLE | RXIF  | TIDLE | TXIF  |

| 01H         | UCR1   | 0000 0X00 | UARTEN | BNO   | PREN  | PRT   | STOPS | TXBRK | RX8   | TX8   |

| 02H         | UCR2   | 0000 0000 | TXEN   | RXEN  | BRGH  | ADDEN | WAKE  | RIE   | TIIE  | TEIE  |

| 03H         | BRG    | XXXX XXXX | BRG7   | BRG6  | BRG5  | BRG4  | BRG3  | BRG2  | BRG1  | BRG0  |

| 04H         | UCR3   | 0         | URST   | _     | _     | _     | _     |       | _     |       |

| 05H~<br>07H | Unused |           |        |       |       | Reser | ved   |       |       |       |

#### **UART Register Summary**

#### • USR Register

The USR register is the status register for the UART, which can be read by the application program to determine the present status of the UART. All flags within the USR register are read only. Further explanation on each of the flags is given below:

| Bit  | 7    | 6  | 5    | 4    | 3     | 2    | 1     | 0    |

|------|------|----|------|------|-------|------|-------|------|

| Name | PERR | NF | FERR | OERR | RIDLE | RXIF | TIDLE | TXIF |

| R/W  | R    | R  | R    | R    | R     | R    | R     | R    |

| POR  | 0    | 0  | 0    | 0    | 1     | 0    | 1     | 1    |

Bit 7

#### **PERR**: Parity error flag 0: no parity error is detected

1: parity error is detected

The PERR flag is the parity error flag. When this read only flag is "0", it indicates a parity error has not been detected. When the flag is "1", it indicates that the parity of the received word is incorrect. This error flag is applicable only if Parity mode (odd or even) is selected. The flag can also be cleared by a software sequence which involves a read to the status register USR followed by an access to the RXR data register.

#### Bit 6 NF: Noise flag

0: no noise is detected

1: noise is detected

The NR flag is the noise flag. When this read only flag is "0", it indicates no noise condition. When the flag is "1", it indicates that the UART has detected noise on the receiver input. The NF flag is set during the same cycle as the RXIF flag but will not be set in the case of as overrun. The NF flag can be cleared by a software sequence which will involve a read to the status register USR followed by an access to the RXR data register.

| Bit 5 | <ul> <li>FERR: Framing error flag</li> <li>0: no framing error is detected</li> <li>1: framing error is detected</li> <li>The FERR flag is the framing error flag. When this read only flag is "0", it indicates that there is no framing error. When the flag is "1", it indicates that a framing error has been detected for the current character. The flag can also be cleared by a software sequence which will involve a read to the status register USR followed by an access to the RXR data register.</li> </ul>                                                                                                                                                                                                                                                                                                                                        |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 4 | <ul> <li>OERR: Overrun error flag</li> <li>0: no overrun error is detected</li> <li>1: overrun error is detected</li> <li>The OERR flag is the overrun error flag which indicates when the receiver buffer has overflowed.</li> <li>When this read only flag is "0", it indicates that there is no overrun error. When the flag is "1", it indicates that an overrun error occurs which will inhibit further transfers to the RXR receive data register. The flag is cleared by a software sequence, which is a read to the status register USR followed by an access to the RXR data register.</li> </ul>                                                                                                                                                                                                                                                       |

| Bit 3 | <ul> <li>RIDLE: Receiver status</li> <li>0: data reception is in progress (data being received)</li> <li>1: no data reception is in progress (receiver is idle)</li> <li>The RIDLE flag is the receiver status flag. When this read only flag is "0", it indicates that the receiver is between the initial detection of the start bit and the completion of the stop bit. When the flag is "1", it indicates that the receiver is idle. Between the completion of the stop bit and the detection of the next start bit, the RIDLE bit is "1" indicating that the UART receiver is idle and the RX pin stays in logic high condition.</li> </ul>                                                                                                                                                                                                                 |

| Bit 2 | <ul> <li>RXIF: Receive RXR data register status</li> <li>0: RXR data register is empty</li> <li>1: RXR data register has available data</li> <li>The RXIF flag is the receive data register status flag. When this read only flag is "0", it indicates that the RXR read data register is empty. When the flag is "1", it indicates that the RXR read data register contains new data. When the contents of the shift register are transferred to the RXR register, an interrupt is generated if RIE=1 in the UCR2 register. If one or more errors are detected in the received word, the appropriate receive-related flags NF, FERR, and/or PERR are set within the same clock cycle. The RXIF flag is cleared when the USR register is read with RXIF set, followed by a read from the RXR register, and if the RXR register has no data available.</li> </ul> |

| Bit 1 | <ul> <li>TIDLE: Transmission idle</li> <li>0: data transmission is in progress (data being transmitted)</li> <li>1: no data transmission is in progress (transmitter is idle)</li> <li>The TIDLE flag is known as the transmission complete flag. When this read only flag is "0", it indicates that a transmission is in progress. This flag will be set to "1" when the TXIF flag is "1" and when there is no transmit data or break character being transmitted. When TIDLE is equal to "1", the TX pin becomes idle with the pin state in logic high condition. The TIDLE flag is cleared by reading the USR register with TIDLE set and then writing to the TXR register. The flag is not generated when a data character or a break is queued and ready to be sent.</li> </ul>                                                                             |

| Bit 0 | <ul> <li>TXIF: Transmit TXR data register status</li> <li>0: character is not transferred to the transmit shift register</li> <li>1: character has transferred to the transmit shift register (TXR data register is empty)</li> <li>The TXIF flag is the transmit data register empty flag. When this read only flag is "0", it indicates that the character is not transferred to the transmitter shift register. When the flag is "1", it indicates that the transmitter shift register has received a character from the TXR data register. The TXIF flag is cleared by reading the UART status register (USR) with TXIF set and then writing to the TXR data register. Note that when the TXEN bit is set, the TXIF flag bit will also be set since the transmit data register is not yet full.</li> </ul>                                                   |

# • UCR1 register

The UCR1 register together with the UCR2 register are the two UART control registers that are used to set the various options for the UART function such as overall on/off control, parity control, data transfer bit length, etc. Further explanation on each of the bits is given below:

| Bit  | 7      | 6   | 5    | 4   | 3     | 2     | 1   | 0             |

|------|--------|-----|------|-----|-------|-------|-----|---------------|

| Name | UARTEN | BNO | PREN | PRT | STOPS | TXBRK | RX8 | TX8           |

| R/W  | R/W    | R/W | R/W  | R/W | R/W   | R/W   | R   | W             |

| POR  | 0      | 0   | 0    | 0   | 0     | 0     | Х   | 0             |

|      |        |     |      |     |       |       |     | <i>II. II</i> |

"x" unknown

|       | "X" unknown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 7 | <ul> <li>UARTEN: UART function enable control</li> <li>0: disable UART. TX and RX pins are in the state of high impedance</li> <li>1: enable UART. TX and RX pins function as UART pins</li> <li>The UARTEN bit is the UART enable bit. When this bit is equal to "0", the UART will be disabled and the RX pin as well as the TX pin will be in the state of high impedance. When the bit is equal to "1", the UART will be enabled and the TX and RX pins will function as defined by the TXEN and RXEN enable control bits. When the UART is disabled, it will empty the buffer so any character remaining in the buffer will be discarded. In addition, the value of the baud rate counter will be reset. If the UART is disabled, all error and status flags will be reset. Also the TXEN, RXEN, TXBRK, RXIF, OERR, FERR, PERR and NF bits will be cleared, while the TIDLE, TXIF and RIDLE bits will be set. Other control bits in UCR1, UCR2 and BRG registers will remain unaffected. If the UART is active and the UARTEN bit is cleared, all pending transmissions and receptions will be terminated and the module will be reset as defined above. When the UART is re-enabled, it will restart in the same configuration.</li> </ul> |

| Bit 6 | <ul> <li>BNO: Number of data transfer bits selection</li> <li>0: 8-bit data transfer</li> <li>1: 9-bit data transfer</li> <li>This bit is used to select the data length format, which can have a choice of either 8-bit or 9-bit format. When this bit is equal to "1", a 9-bit data length format will be selected. If the bit is equal to "0", then an 8-bit data length format will be selected. If 9-bit data length format is selected, then bits RX8 and TX8 will be used to store the 9th bit of the received and transmitted data respectively.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Bit 5 | <ul> <li>PREN: Parity function enable control</li> <li>0: parity function is disabled</li> <li>1: parity function is enabled</li> <li>This is the parity enable bit. When this bit is equal to "1", the parity function will be enabled. If the bit is equal to "0", then the parity function will be disabled.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Bit 4 | <ul> <li>PRT: Parity type selection bit</li> <li>0: even parity for parity generator</li> <li>1: odd parity for parity generator</li> <li>This bit is the parity type selection bit. When this bit is equal to "1", odd parity type will be selected. If the bit is equal to "0", then even parity type will be selected.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Bit 3 | <ul> <li>STOPS: Number of Stop bits selection</li> <li>0: one stop bit format is used</li> <li>1: two stop bits format is used</li> <li>This bit determines if one or two stop bits are to be used. When this bit is equal to "1", two stop bits are used. If this bit is equal to "0", then only one stop bit is used.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Bit 2 | <b>TXBRK</b> : Transmit break character<br>0: no break character is transmitted<br>1: break characters transmit<br>The TXBRK bit is the Transmit Break Character bit. When this bit is "0", there are no break<br>characters and the TX pin operates normally. When the bit is "1", there are transmit break<br>characters and the transmitter will send logic zeros. When this bit is equal to "1", after the<br>buffered data has been transmitted, the transmitter output is held low for a minimum of a 13-bit<br>length and until the TXBRK bit is reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Bit 1 | <b>RX8</b> : Receive data bit 8 for 9-bit data transfer format (read only)<br>This bit is only used if 9-bit data transfers are used, in which case this bit location will store the<br>9th bit of the received data known as RX8. The BNO bit is used to determine whether data<br>transfers are in 8-bit or 9-bit format.      |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 0 | <b>TX8</b> : Transmit data bit 8 for 9-bit data transfer format (write only)<br>This bit is only used if 9-bit data transfers are used, in which case this bit location will store the<br>9th bit of the transmitted data known as TX8. The BNO bit is used to determine whether data<br>transfers are in 8-bit or 9-bit format. |

#### UCR2 register

The UCR2 register is the second of the UART control registers and serves several purposes. One of its main functions is to control the basic enable/disable operation if the UART Transmitter and Receiver as well as enabling the various UART interrupt sources. The register also serves to control the baud rate speed, receiver wake-up function enable and the address detect function enable. Further explanation on each of the bits is given below:

| Bit  | 7    | 6    | 5    | 4     | 3    | 2   | 1    | 0    |

|------|------|------|------|-------|------|-----|------|------|

| Name | TXEN | RXEN | BRGH | ADDEN | WAKE | RIE | TIIE | TEIE |

| R/W  | R/W  | R/W  | R/W  | R/W   | R/W  | R/W | R    | W    |

| POR  | 0    | 0    | 0    | 0     | 1    | 0   | 1    | 1    |

| POR   | 0                                                                                                                         | 0                                                                                                                                                                   | 0                                                                                                                                                                               | 0                                                                                                                                | 1                                                                                                                                    | 0                                                                                               | 1                                                                                                 | 1                                                           |

|-------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Bit 7 | 0: UAR<br>1: UAR<br>The bit n<br>will be dis<br>reset. In<br>"1" and the<br>be contro                                     | T transmitter<br>T transmitter<br>amed TXEN<br>sabled with a<br>this situation<br>he UARTEN<br>illed by the L                                                       | is enabled<br>is the Transr<br>iny pending o<br>the TX pin w<br>bit is also eq<br>JART. Clearir                                                                                 | nitter Enable<br>data transmis<br>vill be in the s<br>ual to "1", th<br>ng the TXEN                                              | Bit. When thesions being a<br>state of high i<br>e transmitter<br>bit during a tansmitter. If the                                    | aborted. In a<br>mpedance. I<br>will be enab<br>ransmission                                     | ddition the b<br>f the TXEN b<br>led and the T<br>will cause th                                   | uffers will be<br>bit is equal to<br>TX pin will<br>le data |

| Bit 6 | RXEN: U<br>0: UAR<br>1: UAR<br>The bit n<br>be disabl<br>be reset.<br>equal to '<br>will be co<br>reception               | ART Receiver<br>receiver is<br>amed RXEN<br>ed with any p<br>In this situat<br>'1" and the L<br>introlled by th                                                     | enabled<br>is the Receiv<br>bending data<br>ion the RX pi<br>JARTEN bit i<br>ne UART. Cle<br>ad and will re                                                                     | ntrol<br>ver Enable B<br>receptions b<br>in will be in tl<br>s also equal<br>earing the R≯                                       | it. When this<br>being aborted<br>ne state of hig<br>to "1", the re-<br>(EN bit during<br>ver. If this situ                          | . In addition<br>gh impedanc<br>ceiver will be<br>g a reception                                 | the receive to<br>the receive to<br>the enabled and<br>the will cause the                         | ouffers will<br>EN bit is<br>d the RX pin                   |

| Bit 5 | BRGH: E<br>0: low s<br>1: high s<br>The bit na<br>together<br>UART. If                                                    | Baud Rate sp<br>peed baud ra<br>speed baud r<br>amed BRGH<br>with the valu                                                                                          | eed selection<br>ate<br>rate<br>selects the l<br>e placed in th<br>ual to "1", the                                                                                              | nigh or low s<br>ne baud rate                                                                                                    | peed mode o<br>register BRG<br>mode is sele                                                                                          | 6, controls the                                                                                 | e Baud Rate                                                                                       | of the                                                      |

| Bit 4 | ADDEN:<br>0: addre<br>1: addre<br>The bit na<br>"1", the a<br>RX7 if BN<br>then the<br>interrupt<br>address b<br>known as | Address det<br>ess detect fur<br>ess detect fur<br>amed ADDE<br>address detect<br>NO=0 or the<br>received wor<br>is enabled, a<br>bit set, which<br>is the 8th or 9 | ect function e<br>nction is disa<br>nction is enal<br>N is the addr<br>ct function is<br>9th bit, which<br>d will be ider<br>n interrupt re<br>is the 8th or<br>th bit of the r | bled<br>bled<br>ess detect fu<br>enabled. Wh<br>a correspond<br>tified as an a<br>equest will be<br>9th bit depe<br>eceived word | nction enable<br>nen it occurs,<br>s to RX8 if Bl<br>address, rath<br>generated e<br>nding on the<br>d is "0" with t<br>the received | if the 8th bit,<br>NO=1, has a<br>er than data.<br>ach time the<br>value of BN0<br>he address o | which corre<br>value of "1",<br>If the corres<br>received wo<br>O. If the addr<br>detect function | sponds to<br>sponding<br>ord has the<br>ress bit            |

| Bit 3 | <ul> <li>WAKE: RX pin falling edge wake-up function enable control</li> <li>0: RX pin wake-up function is disabled</li> <li>1: RX pin wake-up function is enabled</li> <li>This bit enables or disables the receiver wake-up function. If this bit is equal to "1" and the MCU is in IDLE or SLEEP mode, a falling edge on the RX input pin will through INT pin wake-up the device. If this bit is equal to "0" and the MCU is in IDLE or SLEEP mode, any edge transitions on the RX pin will not wake-up the device.</li> </ul>         |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 2 | <b>RIE</b> : Receiver interrupt enable control<br>0: receiver related interrupt is disabled<br>1: receiver related interrupt is enabled<br>This bit enables or disables the receiver interrupt. If this bit is equal to "1" and when the<br>receiver overrun flag OERR or receive data available flag RXIF is set, the UART interrupt request<br>flag will be set. If this bit is equal to "0", the UART interrupt request flag will not be influenced<br>by the condition of the OERR or RXIF flags.                                     |

| Bit 1 | <b>TIIE</b> : Transmitter Idle interrupt enable control<br>0: transmitter idle interrupt is disabled<br>1: transmitter idle interrupt is enabled<br>This bit enables or disables the transmitter idle interrupt. If this bit is equal to "1" and when<br>the transmitter idle flag TIDLE is set, due to a transmitter idle condition, the UART interrupt<br>request flag will be set. If this bit is equal to "0", the UART interrupt request flag will not be<br>influenced by the condition of the TIDLE flag.                          |

| Bit 0 | <ul> <li>TEIE: Transmitter Empty interrupt enable control</li> <li>0: transmitter empty interrupt is disabled</li> <li>1: transmitter empty interrupt is enabled</li> <li>This bit enables or disables the transmitter empty interrupt. If this bit is equal to "1" and when the transmitter empty flag TXIF is set, due to a transmitter empty condition, the UART interrupt request flag will be set. If this bit is equal to "0", the UART interrupt request flag will not be influenced by the condition of the TXIF flag.</li> </ul> |

#### • UCR3 register

The UCR3 register is the last of the UART control registers and controls the software reset operation. The only one available bit named URST in the UART control register UCR3 is the UART software reset control bit. When this bit is equal to "0", the UART operates normally. If this bit is equal to "1", the whole HT45B0F will be reset. When this situation occurs, the transmitter and receiver will be reset. The UART registers including the status register and control registers will keep the POR states shown in the above UART registers table after the reset condition occurs.

| Bit  | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------|------|---|---|---|---|---|---|---|

| Name | URST |   |   |   | _ |   |   |   |

| R/W  | R/W  | _ | _ | _ | _ | _ | _ | _ |

| POR  | 0    |   |   |   |   |   |   | — |

Bit 7 URST: UART software reset 0: no action 1: UART reset occurs Bit 6~0 unimplemented, read as "0"

#### **Baud Rate Generator**

To setup the speed of the serial data communication, the UART function contains its own dedicated baud rate generator. The baud rate is controlled by its own internal free running 8-bit timer, the period of which is determined by two factors. The first of these is the value placed in the baud rate register BRG and the second is the value of the BRGH bit with the control register UCR2. The BRGH bit decides if the baud rate generator is to be used in a high speed mode or low speed mode, which in turn determines the formula that is used to calculate the baud rate. The value N in the BRG register which is used in the following baud rate calculation formula determines the division factor. Note that N is the decimal value placed in the BRG register and has a range of between 0 and 255.

| UCR2 BRGH Bit  | 0          | 1                                      |

|----------------|------------|----------------------------------------|

| Baud Rate (BR) | [64 (N+1)] | <u>f<sub>CLKI</sub><br/>[16 (N+1)]</u> |

By programming the BRGH bit which allows selection of the related formula and programming the required value in the BRG register, the required baud rate can be setup. Note that because the actual baud rate is determined using a discrete value, N, placed in the BRG register, there will be an error associated between the actual and requested value. The following example shows how the BRG register value N and the error value can be calculated.

- · Calculating the baud rate and error values

- For a clock frequency of 4MHz, and with BRGH set to "0" determine the BRG register value N, the actual baud rate and the error value for a desired baud rate of 4800.

- From the above table the desired baud rate BR =  $f_{CL|KL}$

Re-arranging this equation gives N =  $\frac{f_{CLKI}}{(BRx64)} - 1$

Giving a value for N =  $\frac{4000000}{(4800x64)} - 1 = 12.0208$

To obtain the closest value, a decimal value of 12 should be placed into the BRG register. This gives an actual or calculated baud rate value of BR=  $\frac{4000000}{[64(12+1)]} = 4808$

Therefore the error is equal to  $\frac{4808 - 4800}{4800} = 0.16\%$

| Baud  |                         | Baud Rates for BRGH=0 |           |                  |            |           |                             |         |           |  |  |

|-------|-------------------------|-----------------------|-----------|------------------|------------|-----------|-----------------------------|---------|-----------|--|--|

| Rate  | f <sub>CLKI</sub> =4MHz |                       |           | f <sub>CLK</sub> | ı=3.579545 | MHz       | f <sub>CLKI</sub> =7.159MHz |         |           |  |  |

| K/BPS | BRG                     | Kbaud                 | Error (%) | BRG              | Kbaud      | Error (%) | BRG                         | Kbaud   | Error (%) |  |  |

| 0.3   | 207                     | 0.300                 | 0.16      | 185              | 0.300      | 0.00      |                             |         | —         |  |  |

| 1.2   | 51                      | 1.202                 | 0.16      | 46               | 1.190      | -0.83     | 92                          | 1.203   | 0.23      |  |  |

| 2.4   | 25                      | 2.404                 | 0.16      | 22               | 2.432      | 1.32      | 46                          | 2.380   | -0.83     |  |  |

| 4.8   | 12                      | 4.808                 | 0.16      | 11               | 4.661      | -2.90     | 22                          | 4.863   | 1.32      |  |  |

| 9.6   | 6                       | 8.929                 | -6.99     | 5                | 9.321      | -2.90     | 11                          | 9.322   | -2.90     |  |  |

| 19.2  | 2                       | 20.833                | 8.51      | 2                | 18.643     | -2.90     | 5                           | 18.643  | -2.90     |  |  |

| 38.4  | _                       |                       | _         | _                |            | _         | 2                           | 32.286  | -2.90     |  |  |

| 57.6  | 0                       | 62.500                | 8.51      | 0                | 55.930     | -2.90     | 1                           | 55.930  | -2.90     |  |  |

| 115.2 |                         |                       |           |                  |            |           | 0                           | 111.859 | -2.90     |  |  |

The following tables show the actual values of baud rate and error values for the two value of BRGH.

Baud Rates and Error Values for  $\mbox{BRGH}=0$

| Baud  |                         | Baud Rates for BRGH=1 |           |                  |            |           |                             |        |           |  |

|-------|-------------------------|-----------------------|-----------|------------------|------------|-----------|-----------------------------|--------|-----------|--|

| Rate  | f <sub>CLKI</sub> =4MHz |                       |           | f <sub>CLK</sub> | ı=3.579545 | MHz       | f <sub>CLKI</sub> =7.159MHz |        |           |  |

| K/BPS | BRG                     | Kbaud                 | Error (%) | BRG              | Kbaud      | Error (%) | BRG                         | Kbaud  | Error (%) |  |

| 0.3   | _                       | _                     | —         |                  |            |           |                             | _      |           |  |

| 1.2   | 207                     | 1.202                 | 0.16      | 185              | 1.203      | 0.23      |                             |        |           |  |

| 2.4   | 103                     | 2.404                 | 0.16      | 92               | 2.406      | 0.23      | 185                         | 2.406  | 0.23      |  |

| 4.8   | 51                      | 4.808                 | 0.16      | 46               | 4.76       | -0.83     | 92                          | 4.811  | 0.23      |  |

| 9.6   | 25                      | 9.615                 | 0.16      | 22               | 9.727      | 1.32      | 46                          | 9.520  | -0.83     |  |

| 19.2  | 12                      | 19.231                | 0.16      | 11               | 18.643     | -2.90     | 22                          | 19.454 | 1.32      |  |

| 38.4  | 6                       | 35.714                | -6.99     | 5                | 37.286     | -2.90     | 11                          | 37.286 | -2.90     |  |

| 57.6  | 3                       | 62.5                  | 8.51      | 3                | 55.930     | -2.90     | 7                           | 55.930 | -2.90     |  |

| 115.2 | 1                       | 125                   | 8.51      | 1                | 111.86     | -2.90     | 3                           | 111.86 | -2.90     |  |

| 250   | 0                       | 250                   | 0         |                  |            |           | _                           |        |           |  |

#### Baud Rates and Error Values for BRGH = 1

# BRG Register

| Bit  | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|------|

| Name | BRG7 | BRG6 | BRG5 | BRG4 | BRG3 | BRG2 | BRG1 | BRG0 |

| R/W  |

| POR  | х    | х    | х    | х    | х    | х    | х    | х    |

"x": unknown

#### Bit 7~0

# BRG7~BRG0: Baud Rate values

By programming the BRGH bit in UCR2 Register which allows selection of the related formula described above and programming the required value in the BRG register, the required baud rate can be setup.

# **UART Setup and Control**

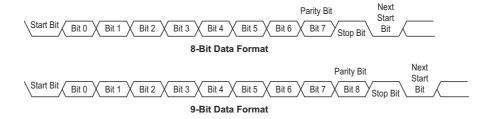

For data transfer, the UART function utilizes a non-return-to-zero, more commonly known as NRZ, format. This is composed of one start bit, eight or nine data bits and one or two stop bits. Parity is supported by the UART hardware and can be setup to be even, odd or no parity. For the most common data format, 8 data bits along with no parity and one stop bit, denoted as 8, N, 1, is used as the default setting, which is the setting at power-on. The number of data bits and stop bits, along with the parity, are setup by programming the corresponding BNO, PRT, PREN and STOPS bits in the UCR1 register. The baud rate used to transmit and receive data is setup using the internal 8-bit baud rate generator, while the data is transmitted and received LSB first. Although the transmitter and receiver of the UART are functionally independent, they both use the same data format and baud rate. In all cases stop bits will be used for data transmission.

• Enabling/Disabling the UART

The basic on/off function of the internal UART function is controlled using the UARTEN bit in the UCR1 register. If the UARTEN, TXEN and RXEN bits are set, then these two UART pins will act as normal TX output pin and RX input pin respectively. If no data is being transmitted on the TX pin, then it will default to a logic high value.

Clearing the UARTEN bit will disable the TX and RX pins and these two pins will be in the state of high impedance. When the UART function is disabled, the buffer will be reset to an empty condition, at the same time discarding any remaining residual data. Disabling the UART will also reset the enable control, the error and status flags with bits TXEN, RXEN, TXBRK, RXIF, OERR, FERR, PERR and NF being cleared while bits TIDLE, TXIF and RIDLE will be set. The remaining control bits in the UCR1, UCR2 and BRG registers will remain unaffected. If the UARTEN bit in the UCR1 register is cleared while the UART is active, then all pending transmissions and receptions will be immediately suspended and the UART will be reset to a condition as defined above. If the UART is then subsequently re-enabled, it will restart again in the same configuration.

- Data, parity and stop bit selection

- The format of the data to be transferred is composed of various factors such as data bit length, parity on/off, parity type, address bits and the number of stop bits. These factors are determined by the setup of various bits within the UCR1 register. The BNO bit controls the number of data bits which can be set to either 8 or 9. The PRT bit controls the choice if odd or even parity. The PREN bit controls the parity on/off function. The STOPS bit decides whether one or two stop bits are to be used. The following table shows various formats for data transmission. The address detect mode control bit identifies the frame as an address character. The number of stop bits, which can be either one or two, is independent of the data length.

| Start<br>Bit                  | Data<br>Bits | Address<br>Bits | Parity<br>Bits | Stop<br>Bit |  |  |  |  |

|-------------------------------|--------------|-----------------|----------------|-------------|--|--|--|--|

| Example of 8-bit Data Formats |              |                 |                |             |  |  |  |  |

| 1                             | 8            | 0               | 0              | 1           |  |  |  |  |

| 1                             | 7            | 0               | 1              | 1           |  |  |  |  |

| 1                             | 7            | 1               | 0              | 1           |  |  |  |  |

| Example                       | of 9-bit Da  | ita Format      | S              |             |  |  |  |  |

| 1                             | 9            | 0               | 0              | 1           |  |  |  |  |

| 1                             | 8            | 0               | 1              | 1           |  |  |  |  |

| 1                             | 8            | 1               | 0              | 1           |  |  |  |  |

#### Transmitter Receiver Data Format

The following diagram shows the transmit and receive waveforms for both 8-bit and 9-bit data formats.

#### • UART transmitter

Data word lengths of either 8 or 9 bits can be selected by programming the BNO bit in the UCR1 register. When BNO bit is set, the word length will be set to 9 bits. In this case the 9th bit, which is the MSB, needs to be stored in the TX8 bit in the UCR1 register. At the transmitter core lies the Transmitter Shift Register, more commonly known as the TSR, whose data is obtained from the transmit data register, which is known as the TXR register. The data to be transmitted is loaded into this TXR register by the application program. The TSR register is not written to with new data until the stop bit from the previous transmission has been sent out. As soon as this stop bit has been transmitted, the TSR can then be loaded with new data from the TXR register, if it is available. It should be noted that the TSR register, unlike many other registers, is not directly mapped into the Data Memory area and as such is not available to the application program for direct read/write operations. An actual transmission of data will normally be enabled when the TXEN bit is set, but the data will not be transmitted until the TXR register has been loaded with data and the baud rate generator has defined a shift clock source. However, the transmission can also be initiated by first loading data into the TXR register, after which the TXEN bit can be set. When a transmission of data begins, the TSR is normally empty, in which case a transfer to the TXR register will result in an immediate transfer to the TSR. If during a transmission the TXEN bit is cleared, the transmission will immediately cease and the transmitter will be reset. The TX output pin will then return to the high impedance state.

Transmitting data

When the UART is transmitting data, the data is shifted on the TX pin from the shift register, with the least significant bit LSB first. In the transmit mode, the TXR register forms a buffer between the internal bus and the transmitter shift register. It should be noted that if 9-bit data format has been selected, then the MSB will be taken from the TX8 bit in the UCR1 register. The steps to initiate a data transfer can be summarized as follows:

- Make the correct selection of the BNO, PRT, PREN and STOPS bits to define the required word length, parity type and number of stop bits.

- Setup the BRG register to select the desired baud rate.

- Set the TXEN bit to ensure that the UART transmitter is enabled and the TX pin is used as a UART transmitter pin.

- Access the USR register and write the data that is to be transmitted into the TXR register. Note that this step will clear the TXIF bit.

This sequence of events can now be repeated to send additional data.

It should be noted that when TXIF=0, data will be inhibited from being written to the TXR register. Clearing the TXIF flag is always achieved using the following software sequence:

- 1. A USR register access

- 2. A TXR register write execution

The read-only TXIF flag is set by the UART hardware and if set indicates that the TXR register is empty and that other data can now be written into the TXR register without overwriting the previous data. If the TEIE bit is set, then the TXIF flag will generate an interrupt. During a data transmission, a write instruction to the TXR register will place the data into the TXR register, which will be copied to the shift register at the end of the present transmission. When there is no data transmission in progress, a write instruction to the TXR register will place the data directly into the shift register, resulting in the commencement of data transmission, and the TXIF bit being immediately set. When a frame transmission is complete, which happens after stop bits are sent or after the break frame, the TIDLE bit will be set. To clear the TIDLE bit the following software sequence is used:

- 1. A USR register access

- 2. A TXR register write execution

Note that both the TXIF and TIDLE bits are cleared by the same software sequence.

Transmitting break

If the TXBRK bit is set, then the break characters will be sent on the next transmission. Break character transmission consists of a start bit, followed by 13×N "0" bits, where N=1, 2, etc. if a break character is to be transmitted, then the TXBRK bit must be first set by the application program and then cleared to generate the stop bits. Transmitting a break character will not generate a transmit interrupt. Note that a break condition length is at least 13 bits long. If the TXBRK bit is continually kept at a logic high level, then the transmitter circuitry will transmit continuous break characters. After the application program has cleared the TXBRK bit, the transmitter will finish transmitting the last break character and subsequently send out one or two stop bits. The automatic logic high at the end of the last break character will ensure that the start bit of the next frame is recognized.

• UART receiver

The UART is capable of receiving word lengths of either 8 or 9 bits can be selected by programming the BNO bit in the UCR1 register. When BNO bit is set, the word length will be set to 9 bits. In this case the 9th bit, which is the MSB, will be stored in the RX8 bit in the UCR1 register. At the receiver core lies the Receiver Shift Register more commonly known as the RSR. The data which is received on the RX external input pin is sent to the data recovery block. The data recovery block operating speed is 16 times that of the baud rate, while the main receive serial shifter operates at the baud rate. After the RX pin is sampled for the stop bit, the received data in RSR is transferred to the receive data register, if the register is empty. The data which is received on the external RX input pin is sampled three times by a majority detect circuit to determine the logic level that has been placed onto the RX pin. It should be noted that the RSR register, unlike many other registers, is not directly mapped into the Data Memory area and as such is not available to the application program for direct read/write operations.

Receiving data

When the UART receiver is receiving data, the data is serially shifted in on the external RX input pin to the shift register, with the least significant bit LSB first. The RXR register is a four byte deep FIFO data buffer, where four bytes can be held in the FIFO while the 5th byte can continue to be received. Note that the application program must ensure that the data is read from RXR before the 5th byte has been completely shifted in, otherwise the 5th byte will be discarded and an overrun error OERR will be subsequently indicated. The steps to initiate a data transfer can be summarized as follows:

- Make the correct selection of the BNO, PRT, PREN and STOPS bits to define the required word length, parity type and number of stop bits.

- Setup the BRG register to select the desired baud rate.

- Set the RXEN bit to ensure that the UART receiver is enabled and the RX pin is used as a UART receiver pin.

At this point the receiver will be enabled which will begin to look for a start bit.

When a character is received, the following sequence of events will occur:

- The RXIF bit in the USR register will be set then RXR register has data available, at least three more character can be read.

- When the contents of the shift register have been transferred to the RXR register and if the RIE bit is set, then an interrupt will be generated.

- If during reception, a frame error, noise error, parity error or an overrun error has been detected, then the error flags can be set.

The RXIF bit can be cleared using the following software sequence:

- 1. A USR register access

- 2. A RXR register read execution

- · Receiving break

Any break character received by the UART will be managed as a framing error. The receiver will count and expect a certain number of bit times as specified by the values programmed into the BNO and STOPS bits. If the break is much longer than 13 bit times, the reception will be considered as complete after the number of bit times specified by BNO and STOPS. The RXIF bit is set, FERR is set, zeros are loaded into the receive data register, interrupts are generated if appropriate and the RIDLE bit is set. If a long break signal has been detected and the receiver has received a start bit, the data bits and the invalid stop bit, which sets the FERR flag, the receiver must wait for a valid stop bit before looking for the next start bit. The receiver will not make the assumption that the break condition on the line is the next start bit. A break is regarded as a character that contains only zeros with the FERR flag set. The break character will be loaded into the buffer and no further data will be received until stop bits are received. It should be noted that the RIDLE read only flag will go high when the stop bits have not yet been received. The reception of a break character on the UART registers will result in the following: